# **Terabit**

Enterprise M.2 80mm PCIE/NVMe Solid State Drive

Data Sheet

# **Revision History**

| Version | Date       | Changes | Note |

|---------|------------|---------|------|

| V001    | 2016-05-28 | Release |      |

|         |            |         |      |

|         |            |         |      |

|         |            |         |      |

|         |            |         |      |

# **Contents**

| 1. Product Features      | 4  |

|--------------------------|----|

| 2. Overview              | 5  |

| 3. Interface             | 5  |

| 4. Physical Dimension    | 6  |

| 5. PIN Description       | 8  |

| 5.1 PIN Location         | 8  |

| 5.2 Signal Description   | 8  |

| 6. Power Consumption     |    |

| 7. Product Reliability   | 10 |

| 7.1. Wear Leveling       | 11 |

| 7.2 ECC                  | 11 |

| 7.3 MTBF                 | 11 |

| 7.4 Bad-block Management | 11 |

| 7.5 S.M.A.R.T Function   | 11 |

| 7.6 TRIM Function        | 11 |

| 8. Performance           | 12 |

| 9. Cache                 | 12 |

| 10. Thermal Sensor       | 12 |

| 11. Certifications       | 13 |

| 12. Ordering Information |    |

| 13. Contact Information  | 14 |

# 1. Product Features

| Interface              | PCle Gen3 x 4                          |

|------------------------|----------------------------------------|

| Form Factor            | M.2 2280                               |

| Dimension              | 80.0 x 22.0 x 3.8 ±0.1(mm)             |

| Capacity               | NAND MLC: 120GB~480GB                  |

| Performance            | Read up to 2500MB/s                    |

|                        | Write up to 1350MB/s                   |

| Power Supply           | D/C 3.3V± 5%                           |

|                        | Standard: 0~+70°C                      |

| Operating Temperature  | Enterprise: -20~+70°C                  |

| Weight                 | <30g                                   |

| Storage Temperature    | -40~+85°C                              |

| Shock                  | Non-operating 1500G peak, 0.5ms        |

|                        | Operating 50G peak, 11ms               |

| Vibration              | 20Hz~80Hz/1.52mm ~ 80Hz-2000Hz/20G     |

|                        | X,Y,Z axis/60min for each              |

| Drop                   | 80cm free falling                      |

| Bending                | ≥20N / Hold 1min/5 times               |

| Burn-in Test           | 36 Hours                               |

|                        | Sequential Reading 5.11W               |

| Max. Power Consumption | Sequential Writing 6.92W               |

|                        | Idle 0.4W                              |

| MTBF                   | 2,000,000 Hours                        |

| • X                    | - Enhanced endurance by dynamic/static |

|                        | wear-leveling                          |

|                        | - Support dynamic power management     |

| Features               | - Support S.M.A.R.T function           |

|                        | - Automatic Bad-block Management       |

| 4.0                    | - Support TRIM and NCQ (Native Command |

|                        | Queuing) Command                       |

| / V)                   | - Support BCH ECC 66bits/1024bytes     |

|                        | - Low Power Management                 |

| Data Retention         | @25°C: 10 years                        |

| Certification          | CE/FCC/RoHS                            |

#### 2. Overview

Terabit M.2 80mm PCIE SSD fully consists of semiconductor devices using original Toshiba NAND MLC Flash, which provide high reliability and high performance for data storage. Terabit M.2 80mm PCIE SSD has standard interface for different applications, and fully conforms to the same mechanical and mounting requirements as standard rotating disk drives. This series of products are designed for premium applications that require both strong reliability and high capacity while installing room is limited such as Embedded Computer, Panel Computer, Enterprise Server, Media Player, Ultra-book and Workstations. With up to 480GB capacity on NAND MLC Flash Terabit M.2 80mm PCIE SSD totally goes through a variety of proofing tests such as Shock Test, Vibration Test and Burn-in Test. Well proved under -20~+70°C temperature and equipped with Power Failure Protect and Over Load Protect, this series of products can work smoothly under Enterprise environments.

#### 3. Interface

Terabit M.2 80mm PCIE Solid State Drive complies PCIe Gen3 x 4 and NVMe 1.2

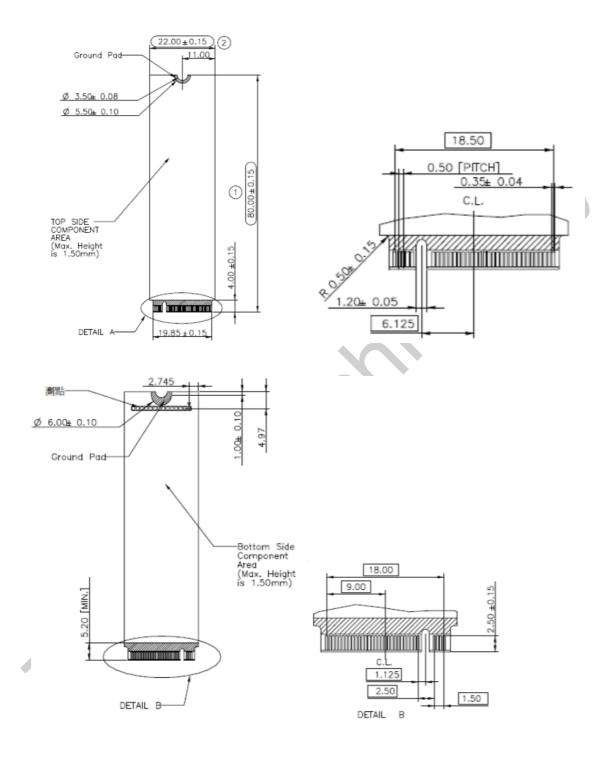

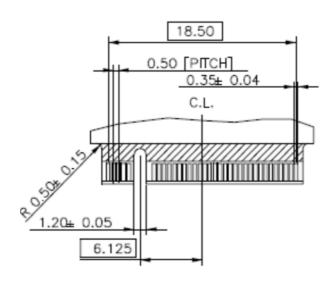

# 4. Physical Dimension

| Parameter | Value | Unit |

|-----------|-------|------|

| Length    | 80.0  | mm   |

| Width     | 22.0  | mm   |

| Thickness | 3.80  | mm   |

# 5. PIN Description

## 5.1 PIN Location

# 5.2 Signal Description

| Pin# | Туре  | Description                                                     | Pin# | Туре       | Description |

|------|-------|-----------------------------------------------------------------|------|------------|-------------|

| 1    | GND   | Ground                                                          | 2    | 3.3V       | 3.3V Source |

| 3    | GND   | Ground                                                          | 4    | 3.3V       | 3.3V Source |

| 5    | PETn3 | PCIe TX Differential signal defined by the PCI Express M.2 spec | 6    | No connect |             |

| 7    | PETp3 | PCIe TX Differential signal defined by the PCI Express M.2 spec | 8    | No connect |             |

| 9    | GND   |                                                                 | 10   | LED1#(O)   |             |

| 11   | PERn3 | PCIe RX Differential signal defined by the PCI Express M.2 spec | 12   | 3.3V       | 3.3V Source |

| 13   | PERp3 | PCIe RX Differential signal defined by the PCI Express M.2 spec | 14   | 3.3V       | 3.3V Source |

| 15   | GND   |                                                                 | 16   | 3.3V       | 3.3V Source |

| 17   | PETn2 | PCIe TX Differential signal defined by the PCI Express M.2 spec | 18   | 3.3V       | 3.3V Source |

| 19   | PETp2 | PCIe TX Differential signal defined                             | 20   | No connect |             |

|    |         |                                                                    | доо. р. | 100 1 112 0 0 11111 1    | CIE Solia State Di Ive                                                                                                         |

|----|---------|--------------------------------------------------------------------|---------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------|

|    |         | by the PCI Express M.2 spec                                        |         |                          |                                                                                                                                |

| 21 | GND     |                                                                    | 22      | No connect               |                                                                                                                                |

| 23 | PERn2   | PCIe RX Differential signal defined by the PCI Express M.2 spec    | 24      | No connect               |                                                                                                                                |

| 25 | PERp2   | PCIe RX Differential signal defined by the PCI Express M.2 spec    | 26      | No connect               |                                                                                                                                |

| 27 | GND     |                                                                    | 28      | No connect               |                                                                                                                                |

| 29 | PETn1   | PCIe TX Differential signal defined by the PCI Express M.2 spec    | 30      | No connect               |                                                                                                                                |

| 31 | PETp1   | PCIe TX Differential signal defined by the PCI Express M.2 spec    | 32      | No connect               | 703                                                                                                                            |

| 33 | GND     |                                                                    | 34      | No connect               |                                                                                                                                |

| 35 | PERn1   | PCIe RX Differential signal defined by the PCI Express M.2 spec    | 36      | No connect               |                                                                                                                                |

| 37 | PERp1   | PCIe RX Differential signal defined by the PCI Express M.2 spec    | 38      | No connect               |                                                                                                                                |

| 39 | GND     |                                                                    | 40      | No connect               |                                                                                                                                |

| 41 | PETn0   | PCIe TX Differential signal defined<br>by the PCI Express M.2 spec | 42      | No connect               |                                                                                                                                |

| 43 | РЕТр0   | PCIe TX Differential signal defined by the PCI Express M.2 spec    | 44      | No connect               |                                                                                                                                |

| 45 | GND     |                                                                    | 46      | No connect               |                                                                                                                                |

| 47 | PERn0   | PCIe RX Differential signal defined by the PCI Express M.2 spec    | 48      | No connect               |                                                                                                                                |

| 49 | PERp0   | PCIe RX Differential signal defined<br>by the PCI Express M.2 spec | 50      | PERST#(I)(0/<br>3.3V)    | PE-Reset is a functional reset to the card as defined by the PCle Mini CEM specification.                                      |

| 51 | GND     |                                                                    | 52      | CLKREQ#(I/O<br>)(0/3.3V) | Clock Request is a reference clock request signal as defined by the PCIe Mini CEM specification; Also used by L1 PM Substates. |

| 53 | REFCLKn | PCIe Reference Clock signals (100 MHz) defined by the PCI Express  | 54      | PEWAKE#(I/               | PCIe PME Wake. Open Drain with                                                                                                 |

# **Terabit**

# Enterprise M.2 80mm PCIE Solid State Drive

|    | 1                      |                                                                             | Litterpi | 130 14.2 00111111 1              | CIE Solia State Drive                                                                                                               |

|----|------------------------|-----------------------------------------------------------------------------|----------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

|    |                        | M.2 spec.                                                                   |          | O)(0/3.3V)                       | pull up on platform; Active Low.                                                                                                    |

| 55 | REFCLKp                | PCIe Reference Clock signals (100 MHz) defined by the PCI Express M.2 spec. | 56       | Reserved for<br>MFG DATA         | Manufacturing Data line. Used for SSD manufacturing only. Not used in normal operation. Pins should be left N/C in platform Socket. |

| 57 | GND                    |                                                                             | 58       | Reserved for<br>MFG CLOCK        |                                                                                                                                     |

| 59 | Module<br>Key          |                                                                             | 60       | Module Key                       | (0)                                                                                                                                 |

| 61 | Module<br>Key          |                                                                             | 62       | Module Key                       |                                                                                                                                     |

| 63 | Module<br>Key          |                                                                             | 64       | Module Key                       |                                                                                                                                     |

| 65 | Module<br>Key          |                                                                             | 66       | Module Key                       |                                                                                                                                     |

| 67 | No<br>connect          |                                                                             | 68       | SUSCLK(32K<br>Hz)<br>(I)(0/3.3V) | 32.768 kHz clock supply input that is provided by the platform chipset to reduce power and cost for the module.                     |

| 69 | PEDET<br>(NC-PCI<br>e) | Host I/F Indication; No Connect for PCIe.                                   | 70       | 3.3V                             | 3.3V Source                                                                                                                         |

| 71 | GND                    |                                                                             | 72       | 3.3V                             | 3.3V Source                                                                                                                         |

| 73 | GND                    |                                                                             | 74       | 3.3V                             | 3.3V Source @0.5 Amps                                                                                                               |

| 75 | GND                    | v                                                                           |          |                                  |                                                                                                                                     |

## 6. Power Consumption

| Capacity | Idle | Read | Write | Unit |

|----------|------|------|-------|------|

| 120GB    | 0.40 | 4.44 | 3.37  | W    |

| 240GB    | 0.40 | 4.89 | 4.81  | W    |

| 480GB    | 0.40 | 5.11 | 6.92  | W    |

## 7. Product Reliability

#### NAND MLC Flash:

| Capacity | Endurance           | Data Retention | MTBF      | Warranty |

|----------|---------------------|----------------|-----------|----------|

|          | Total Bytes Written |                |           |          |

| 120GB    | Up to 175TB         |                |           |          |

| 240GB    | Up to 349TB         | @25°C          | 2 Million | 3 Years  |

| 480GB    | Up to 698TB         | >10 Years      | Hours     | Limited  |

<sup>\*</sup>Total Bytes Written= 【(Flash P/E cycle) x (number of bits in drive)】/WAI WAI=1.428704724

#### 7.1 Wear-Leveling

Terabit M.2 80mm PCIE SSD supports both static and dynamic wear-leveling technology. These two algorithms guarantee each block of flash memory at same level of erase cycles to improve lifetime limitation of NAND based storage.

#### 7.2 ECC

ECC (Error Correction Code): Enhanced configurable BCH ECC engine. Terabit M.2 80mm PCIE SSD implements the BCH ECC Algorithm, which is one of the most powerful ECC algorithms in the industry. This algorithm can correct up to 60 random bit errors in each 512 bytes.

#### **7.3 MTBF**

Mean time between failures (MTBFs) for the SSD can be predicted based on the component reliability data using the methods referenced in the reliability prediction procedures for electronic equipment, the prediction result for this SSD is more than 2,000,000 hours.

#### 7.4 Bad-block Management

Terabit implements an efficient bad block management algorithm into the SSD to detect factory produced bad blocks as well as those that develop over the lifetime of the device. This process is completely transparent to the user through the use of S.M.A.R.T. command tools, i.e., the user will not be aware of the existence of the bad blocks during operation.

#### 7.5 S.M.A.R.T Function

S.M.A.R.T stands for Self-Monitoring, Analysis and Reporting Technology. This technology enables the PC to predict the future failure of hard disk drives. Through the S.M.A.R.T. system, Terabit M.2 80mm PCIE SSD incorporates a suite of advanced diagnostics that monitor the internal operation of the drive and provide an early warning for many types of potential problems. When a potential problem is detected, the SSD can be repaired or replaced before any data is lost or damaged.

#### 7.6 TRIM Function

Terabit Solid State Drive equips built-in TRIM function, and it helps collect and clean data garbage, which keeps the system in a high performance status even after long-term using.

# 8. Performance

| Capacity | Sequential R(max) | Sequential W(max) | IOPS Read (max) | IOPS Write (max) |

|----------|-------------------|-------------------|-----------------|------------------|

| 120GB    | 2300MB/s          | 450MB/s           | 220,000         | 130,000          |

| 240GB    | 2400MB/s          | 850MB/s           | 270,000         | 160,000          |

| 480GB    | 2500MB/s          | 1350MB/s          | 300,000         | 200,000          |

$<sup>{\</sup>it *Performance will vary due\ to\ different\ platform\ and\ software}$

## 9. Cache

| Cache   | DDR2 | DDR3 | Capacity |

|---------|------|------|----------|

| Support | /    | Yes  |          |

## 10. Thermal Sensor

| Temperature Sensor | Yes     | 1 | No |

|--------------------|---------|---|----|

|                    | Support |   | /  |

# 11. Certifications

EN 55022:2010

EN: 55024:2010

EN 61000-3-2:2013

EN 61000-3-3:2014

47 CFR, Part2, Part15, CISPR PUB.22

With reference to RoHS Directive 2011/65/EU recasting 2002/95/EC

# 12. Ordering information

| Series                          | *Model Name      | Capacity | Flash    | Length |

|---------------------------------|------------------|----------|----------|--------|

| Enterprise M.2 80mm<br>PCIE SSD | E80PCIXTMLC-120G | 120GB    | NAND MLC | 80mm   |

|                                 | E80PCIXTMLC-240G | 240GB    | NAND MLC | 80mm   |

|                                 | E80PCIXTMLC-480G | 480GB    | NAND MLC | 80mm   |

<sup>\*</sup>XT refers to temperature range, ST refers to standard temperature, CT refers to enterprise temperature.

## 13. Contact Information

Shanghai Terabit Technology Co., Ltd

Telephone: +86.21.34303488

Fax: +86.21.34303488

Email: sales@terabitsys.com Website: www.terabitsys.com

Address: #513, No.38 Building, Wanke VMO, No. 2049 Pujin Road, Pujiang Town, Minhang

District, Shanghai, 201112 P.R. China